# Reducing SSD Read Latency via NAND Flash Program and Erase Suspension

Guanying Wu and Xubin He

Department of Electrical and Computer Engineering, Virginia Commonwealth University, Richmond, Virginia {wug, xhe2}@vcu.edu

## Introduction

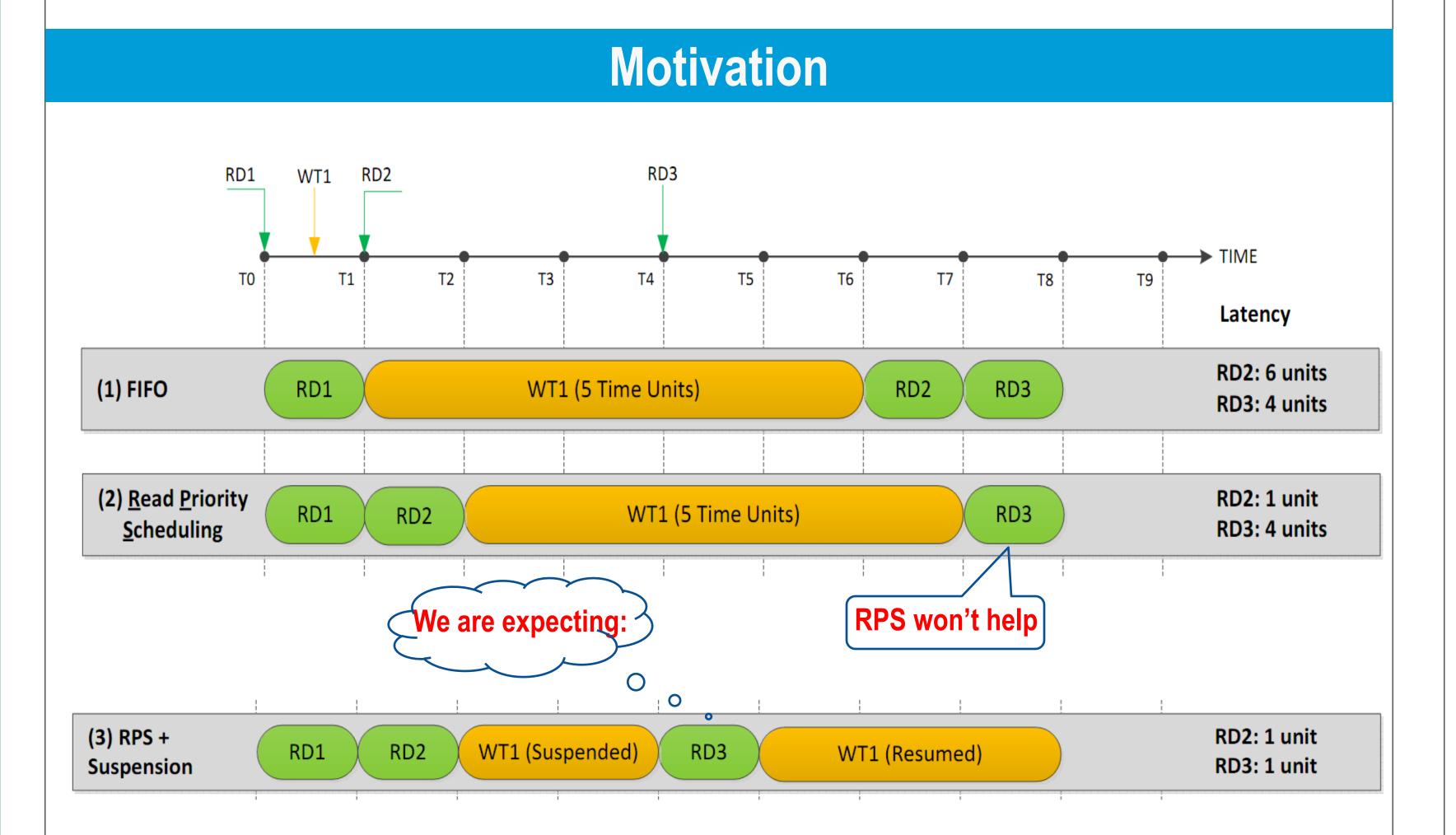

In NAND flash memory, the program or erase (P/E) operations are non-suspendable. Therefore, the subsequent read requests have to wait until the time-consuming P/E operations to complete. This problem could increase the read latency by 2x. Inspired by the internal mechanism of NAND flash P/E algorithms, we propose a low-overhead P/E suspension scheme to reduce SSD read latency.

# Background

#### References

- ➤ AGRAWAL, N., et. al. Design Trade-offs for SSD Performance. In USENIX ATC (Boston, Massachusetts, USA, 2008). ➤ ARASE, K. Semiconductor NAND Type Flash Memory with Incremental Step Pulse Programming, Sept. 22 1998. U.S. Patent 5,812,457.

- ➤BREWER, J., et al. *Nonvolatile Memory Technologies with Emphasis on Flash*. IEEE Whiley-Interscience, Berlin(2007). ➤DIMITRIJEVIC, Z., RANGASWAMI, R., AND CHANG, E. Design and Implementation of Semi-preemptible IO. In FAST(2003), USENIX, pp. 145–158.

- ➤QURESHI, M., et al. Improving Read Performance of Phase Change Memories via Write Cancellation and Write Pausing. In HPCA (2010), IEEE, pp. 1–11.

### Acknowledgement

This research is sponsored in part by the U.S. National Science Foundation (NSF) under grants CCF-1102605 and CCF-1102624.

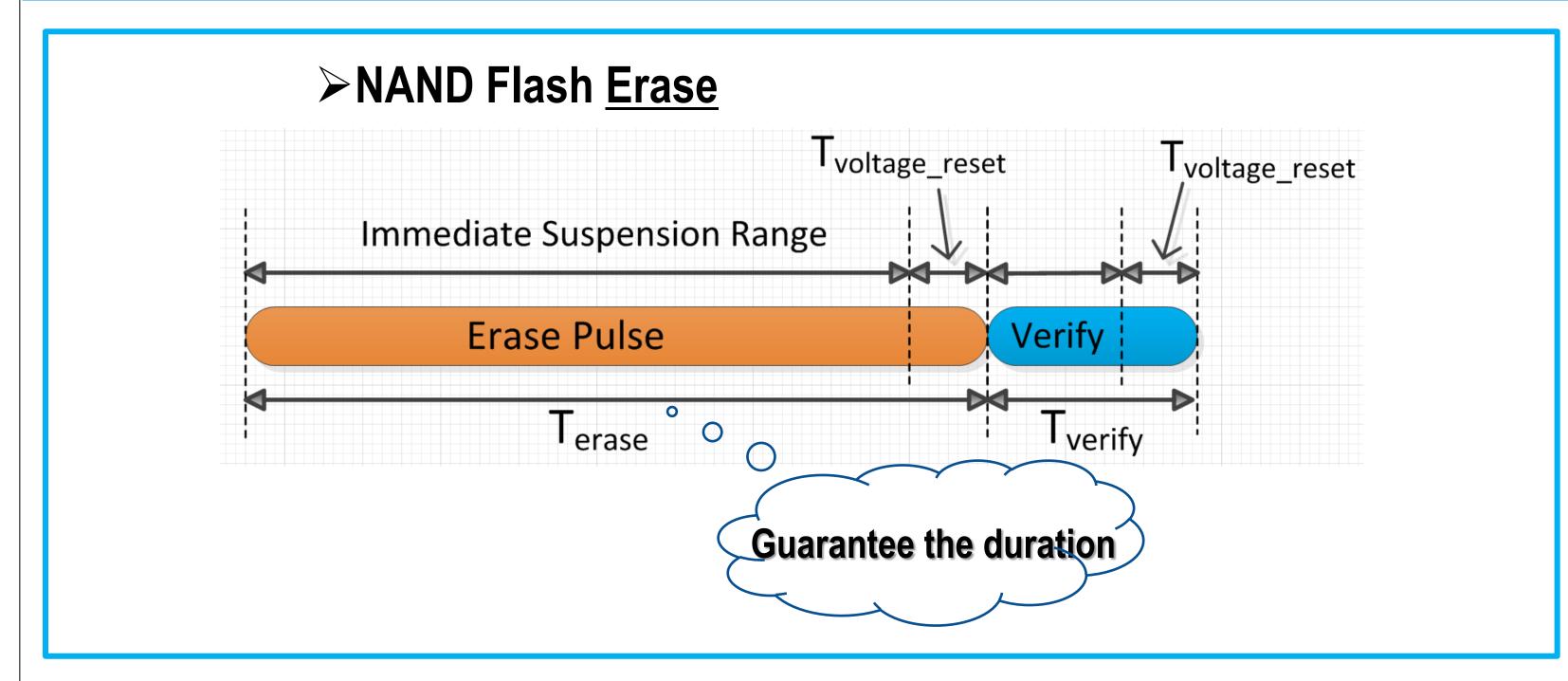

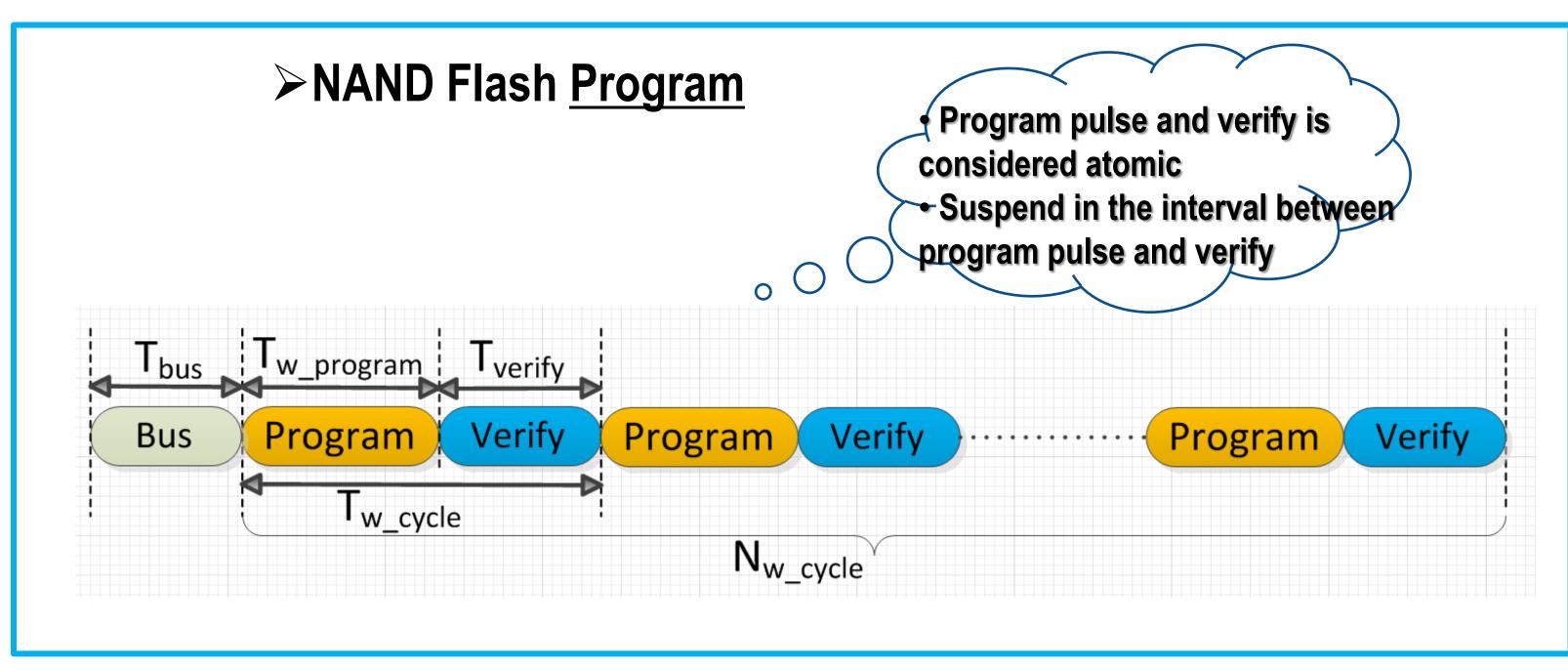

# Design >Suspend/Resume Erase □Case 1: Read arrives when resetting wire voltage voltage\_reset Immediate Suspension Range **Erase Pulse** Suspension Point Read Arrival □Case 2: Read arrives at Immediate Suspension Range voltage\_reset **Erase Pulse** Read **Suspension Point** Read Arrival >Suspend/Resume Erase □Case 1: Suspension happens at **Verify** phase ✓ Redo Verify phase. (overhead to erase latency) □Case 2: Suspension happens at **Erase** phase ✓ Finish what is left before suspension. >Suspend/Resume Program □Choice 1: Suspend in the intervals – Inter-Phase-Suspension Read Arrival Program Verify Program Verify Verify Program \ -Suspension Point Read Arrival Suspension Point □ Choice 2: Cancel the current phase – Intra-Phase-Cancellation Voltage reset P/V Cancelled Read Suspension Point >Suspend/Resume Program ☐Resume from **IPS** buffer

#### Resumption Point ☐ Resume from IPC Re-do PROG Buffer Verify Verify Resumption Point

Verify/Program

**Evaluation**

Buffer

Read

Read

# Conclusion

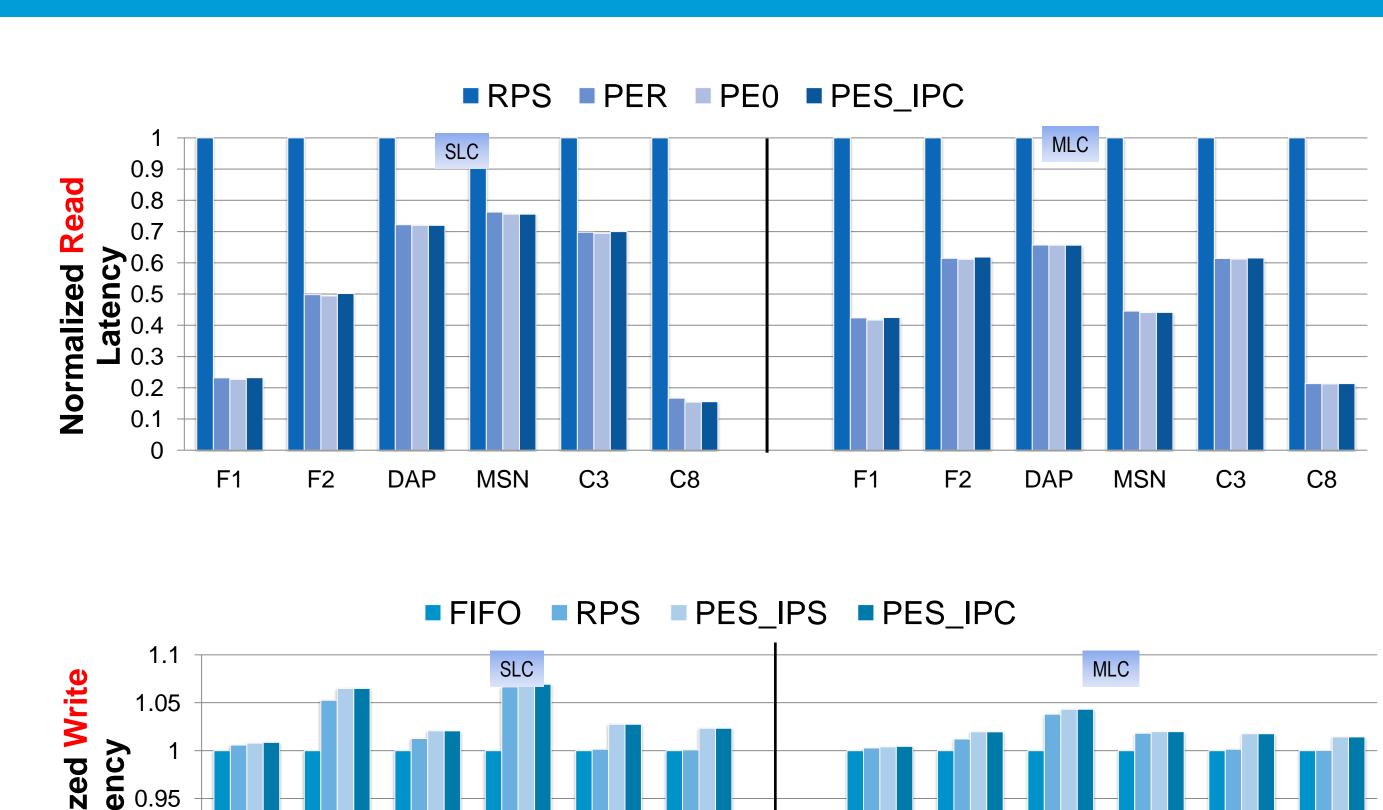

- **■**Suspending P/E for read is achievable.

- **✓** Easy to implement.

- ✓ Significant read performance gain.

- **✓ Low overhead on write latency.**

Program/Verify

(P/V cancelled)